# SNIP: Speculative Execution and Non-Interference Preservation for Compiler Transformations

SÖREN VAN DER WALL, TU Braunschweig, Germany ROLAND MEYER, TU Braunschweig, Germany

We address the problem of preserving non-interference across compiler transformations *under speculative semantics*. We develop a proof method that ensures the preservation uniformly across all source programs. The basis of our proof method is a new form of simulation relation. It operates over directives that model the attacker's control over the micro-architectural state, and it accounts for the fact that the compiler transformation may change the influence of the micro-architectural state on the execution (and hence the directives). Using our proof method, we show the correctness of dead code elimination. When we tried to prove register allocation correct, we identified a previously unknown weakness that introduces violations to non-interference. We have confirmed the weakness for a mainstream compiler on code from the libsodium cryptographic library. To reclaim security once more, we develop a novel static analysis that operates on a product of source program and register-allocated program. Using the analysis, we present an automated fix to existing register allocation implementations. We prove the correctness of the fixed register allocations with our proof method.

CCS Concepts: • Security and privacy  $\rightarrow$  Formal security models; Side-channel analysis and countermeasures; • Software and its engineering  $\rightarrow$  Compilers.

Additional Key Words and Phrases: speculative execution, compilation, verification, register allocation

## **ACM Reference Format:**

Sören van der Wall and Roland Meyer. 2025. SNIP: Speculative Execution and Non-Interference Preservation for Compiler Transformations. *Proc. ACM Program. Lang.* 9, POPL, Article 51 (January 2025), 39 pages. https://doi.org/10.1145/3704887

## 1 Introduction

Cryptographic implementations must satisfy two conflicting requirements: They must compute highly performant to be of practical use and be absolutely secure for use in critical systems. Implementations optimize performance with knowledge about underlying micro-architectural hardware features such as memory access patterns that improve cache usage. Security, however, is threatened by side-channel attacks that exploit precisely these hardware features to leak sensitive information [Brumley and Boneh 2005]. To mitigate side-channel attacks, leakage of sensitive data needs to be eliminated. This confronts the programmer with two challenges: First, semantics of source-level languages do not model leaks produced by side-channels [Vu et al. 2021]. And second, even if the source-level code is secure, incautious implementation of compiler optimizations can insert new leakage, rendering efforts to secure the source program useless [Simon et al. 2018; Barthe, Blazy, Grégoire, et al. 2019]. Developers address these problems with coding guidelines such as constant time programming and disabling compiler optimizations. But following the guidelines is non-trivial and overlooked mistakes corrupt the guarantee for security [Al Fardan and Paterson

Authors' Contact Information: Sören van der Wall, TU Braunschweig, Braunschweig, Germany, s.van-der-wall@tu-bs.de; Roland Meyer, TU Braunschweig, Braunschweig, Germany, roland.meyer@tu-bs.de.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for third-party components of this work must be honored. For all other uses, contact the owner/author(s).

© 2025 Copyright held by the owner/author(s).

ACM 2475-1421/2025/1-ART51

https://doi.org/10.1145/3704887

```

chacha20(..., uint8* sec, uint8 bytes) {

Code Stack (-SP)

uint8 buf[8];

0x48

stk[0] = bytes;

0x40

buf

for (i = 0; i < 8; i++)

Heap

{ buf[i] = sec[i]; }

0xE0

sensitive

bytes = stk[0];

0xC8

sec

data

if (bytes < 64) {...} ... }

0xC0

```

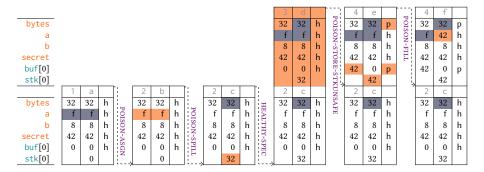

Code 1. Spectre-PHT. Registers are orange and memory variables teal. The stack contents are shifted by the stack pointer to appear constant. Framed instructions were inserted by register allocation.

2013]. At the same time, disabling compiler optimizations is dissatisfactory. Formal methods have shown to help with the challenges: The first challenge is overcome with novel leakage semantics that model side-channel leakage within the programming language's semantics [Molnar et al. 2006; Barthe, Betarte, et al. 2014]. For the second, novel proof methods for compilers under leakage semantics provide a guarantee that side-channel security of the source program carries over to the executable [Barthe, Grégoire, and Laporte 2018; Barthe, Blazy, Grégoire, et al. 2019; Barthe, Blazy, Hutin, et al. 2021; Barthe, Grégoire, Laporte, and Priya 2021]. Sadly, the recent discovery of Spectre attacks [Canella et al. 2019; Kocher et al. 2019] again presents a hardware feature that leakage semantics fall short of: *Speculative execution* produces side-channel leakages not captured by leakage semantics. This means both challenges were open again, and the verification community was quick to address the first: The development of speculative execution semantics has already taken place [Cauligi, Disselkoen, Gleissenthall, et al. 2020; Guarnieri, Köpf, Reineke, et al. 2021], and formal tools find speculative side-channel leakages or even prove their absence (cf. Section 7). Provably correct compilation under speculative execution semantics, however, remains an unsolved challenge that we address in this paper. It is the challenge that we address in this paper.

# 1.1 Background

Before we detail our contributions, we position our paper in the field of *formally verified cryptogra*phy and provide background on *Spectre attacks* and *mitigations*. We outline *speculative execution semantics*, *non-interference* as the property that guarantees a program's side-channel security even under speculation, and *provably correct compilation* for leakage semantics without speculation.

Formally verified cryptography. The field of formally verified cryptography aims to provide cryptographic implementations that are secured not only by trust in the developer but in a machine-checkable proof of correctness and security. In order to achieve this goal, implementations are carefully crafted and three main areas of research pursue different subgoals [Barbosa et al. 2021]:

(i) Cryptographic protocol design aims to provide proofs that the cryptographic protocol in itself does not reveal secrets to adversarial protocol participants, among other properties. (ii) Correct and performant implementation of the protocol aims to prove the implementation functionally correct. (iii) Implementation security investigates the compilation of implementations and the execution of binaries on real hardware in order to prove the absence of attacks that stem from the discrepancy between idealized program semantics and actual hardware semantics. This paper belongs to (iii): We assume that source programs correctly implement formally verified protocols, i.e. steps (i) and (ii) are completed. We investigate whether compiler transformations preserve side-channel security. To that end, our formal semantics models side-channel leakages and speculative execution, the micro-architectural hardware components that enable the recently discovered Spectre attacks.

Spectre attacks and mitigations. Spectre attacks observe side-channel leakages that are produced during speculative execution. Speculative execution allows the processor to speculatively execute instructions from the pipeline even though they still have unevaluated instruction parameters. When the processor detects a misspeculation, i.e. it assumed incorrect values for the unevaluated parameters, it rolls back execution to erase its effect. Rollbacks are invisible to typical source-level semantics, but parts of the micro-architecture such as the cache-state are not reverted. This creates side-channel leakage observable to an attacker during the speculative execution of instructions. Spectre attacks target this in the following way: (i) Train some micro-architectural component to speculatively execute a code fragment that (ii) under misspeculation brings sensitive data into a processor's register, which (iii) is leaked through side-channels. The prominent example is Spectre-PHT [Kocher et al. 2019], whose source of speculation is the processor's branch prediction unit (Prediction History Table), and the side-channel leakage happens via the cache [Yarom and Falkner 2014; Liu et al. 2015] or the program counter [Molnar et al. 2006]. Code 1 demonstrates the attack: The code is intended to load an 8-byte chunk from sec, which points into a stream of sensitive data, and to store it into a stack-local buffer buf in order to later perform computation on it. (i) The attacker might train the branch predictor in a way that it speculates the for-conditional in Line 4 and executes Line 5 an additional time even though i = 8. Line 5 then stores sensitive data from &sec + 8, say v, to &buf + 8 which aliases with &buf + 8 = &stk. The speculative execution might continue with Line 7, where (ii) v is loaded into bytes. (iii) The register is then used in Line 8, where the branching condition is leaked, disclosing to the attacker whether v < 64.

The de facto approach to avoid Spectre attacks are hardware and software mitigations. In hardware, a simple mitigation is to disable specific speculation sources using control registers. This penalizes performance as it disables the optimization for the whole program, even when other parts of the program do not operate on sensitive data. Software mitigations have received more attention, especially for branch prediction (Spectre-PHT, cf. Section 7, Tools), because disabling branch prediction has severe impact on performance [Vassena et al. 2021, Evaluation]. Spectre-PHT has two known software mitigations: Speculation fence insertion and speculative load hardening [Zhang et al. 2023; Carruth 2024]. Speculation fences sfence instruct the processor to stop speculation and wait until all instruction's unevaluated parameters are resolved before either continuing computation in case of a correct prediction or rolling back in case of a misprediction. This prevents instructions following sfence to be executed speculatively altogether.<sup>2</sup> The mitigation is applicable to all known kinds of speculation sources. Speculative load hardening slh a is a mitigation unique to branch prediction. Executing slh a wipes the contents of register a in case of a branch misprediction, but does not stop speculative execution. In case of correct prediction or non-speculative execution, it leaves the register contents unchanged. In the binary, this semantics is achieved by tying the contents of a to a previous branching condition cond via a data dependency (in the sense of a := cond ? a := 0). This forces the processor to evaluate cond before assigning a value to a. The processor is not guaranteed to stop speculation immediately upon learning the correct value for cond, but the value in a is now safe to be leaked. For other speculation sources (Section 7, Speculation Sources), speculative load hardening does not work because no similar data dependency is known. The Spectre attack from Code 1 is mitigated by inserting either sfence or slh bytes between Line 7 and 8.

$<sup>^{1}</sup>$ The attack on this code is unlikely to execute on actual hardware because the specific speculation patterns would be hard to train. We chose it because it also demonstrates a new vulnerability in register allocation that we present in this paper.  $^{2}$ This is idealized: In ×86, for example, the instruction is realized with a memory fence LFENCE, which only executes after all loaded parameters to instructions are resolved - stopping the so far known speculation sources.

<sup>&</sup>lt;sup>3</sup>In x86, a cmov instruction is used which does not introduce control-flow branching, so branch prediction will not speculate.

Speculative execution semantics and Non-interference. Speculative execution semantics extend leakage semantics by speculation. The achievement of leakage semantics is to incorporate a model leakage observable to the attacker in the semantics. The observable side-channel leakage depends on the leakage model. Common is the constant-time model which exposes the addresses of memory accesses and the program counter as leakage to the attacker [Barthe, Betarte, et al. 2014; Guarnieri, Köpf, Reineke, et al. 2021]. Transitions in leakage semantics (without speculation) are of the form  $s \to t$ . They prompt a transition from  $s \to t$  while capturing attacker-visible effects on the microarchitectural state in the *leakage observation*  $\lambda$ . Side-channel security can now be formulated as a property on the program's leakage semantics. For that, a relation declares initial states as indistinguishable to the attacker when they differ only w.r.t. sensitive data unknown to the attacker. The property is non-interference, which requires that the executions from indistinguishable initial states produce equal leakages. Non-interference guarantees side-channel security: leakages cannot depend on sensitive data in any way. Without speculation, the running example Code 1 satisfies non-interference under the constant-time leakage model: The control flow is not dependent on the secret sec and the addresses of memory accesses (Lines 3, 5, and 7) are independent as well.

The extension to speculative execution semantics came with a new challenge: Non-determinism. Whether the processor mispredicts and when it detects misprediction is highly hardware dependent and potentially even under the attacker's influence. As a result, there is not a single execution but instead a set of possible executions, each with a different sequence of leakages. A transition in speculative execution semantics is of the form  $s \xrightarrow{\delta:\lambda} t$ . Again,  $\lambda$  is the attacker-observable leakage. What is new is the *directive*  $\delta$  that models the attacker's control over speculation [Cauligi, Disselkoen, Gleissenthall, et al. 2020; Barthe, Cauligi, et al. 2021]. The directives determine the program's speculation behavior. They provide an abstraction of the micro-architecture that the attacker can use to steer the execution whenever it depends on the micro-architectural state. In our example, the attacker steers speculation with the following sequence of directives in order to lead execution to the leakage of sensitive data:

$$\bullet \qquad . \qquad \left( \text{BR} . \bullet \right)^8 \qquad . \qquad \text{SP} \qquad . \qquad \text{SU stk 0} \qquad . \qquad \text{BR} . \bullet . \bullet \qquad . \\ \text{Line 3} \qquad \qquad \text{Line 4} \qquad \qquad \text{Line 5} \qquad \qquad \text{Lines 4, 7, and 8}$$

The intuition is the following. The first instruction is a memory access which cannot be influenced by the attacker, denoted by the directive •. Then, the attacker steers execution so that the correct branch is taken 8 times: Directive BR executes the correct branch and • executes the memory assignment inside the loop. The attacker then chooses to begin a misspeculation with directive SP which enters the loop once more. This leads to an unsafe memory access during the additional loop iteration, where we let the attacker choose actual memory location with SU Stk 0. The remaining sequence leads the execution to the leaking instruction.

In order to phrase non-interference on speculative execution semantics, the idea is to compare executions where the sequence of directives along the executions are equal. Then, the attacker trained the hardware in the same way and can be sure that observed differences in leakage are due to sensitive data. We define our speculative execution semantics (Section 2) and non-interference property (Section 3) in this spirit.

Secure compilation. The goal of secure compilation is to prove that a compiler pass preserves non-interference from source to target program. The current methods for leakage semantics without speculation draw from classical methods for compiler correctness which utilize *simulation* in order to argue that the target program's executions can be found in the source program's semantics [McCarthy and Painter 1967; Leroy 2009]. A traditional simulation is a relation  $\prec$  between the target program's states and the source program's states. Whenever a target state t is simulated by a source state s,  $t \prec s$ , and has a transition  $t \stackrel{o}{\longrightarrow} v$ , where o is an observable environment

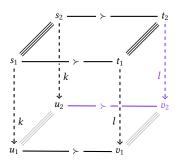

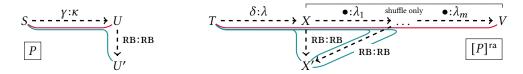

Fig. 1. Constant-time cubes. Left: leakage transforming; Right: directive transforming (◄).

interaction, then s has to have a next transition  $s \xrightarrow{o} u$  so that  $v \prec u$ . Simulation ensures that the target program's execution produces the same observable environment interactions as the source program. For leakage semantics, a notion of simulation needs more: Compilers aim to preserve observable environment interactions such as system-calls, but they regularly modify side-channel leakage which creates a difference in leakage between source and target program. Leakage transformation [Costanzo et al. 2016; Barthe, Grégoire, and Laporte 2018; Barthe, Grégoire, Laporte, and Priya 2021] solves this issue: Given the leakages along a source program's execution, the simulation also provides a way to transform the observable leakage into the observable leakage of the corresponding target program's execution. In order to preserve non-interference, a simulation with leakage transformation needs to satisfy the constant-time cube diagram. The cube diagram can be seen in Figure 1 on the left. It looks at two pairs of states related by simulation  $t_1 \prec s_1$  and  $t_2 \prec s_2$ . Then, if  $s_1$ 's next transitions leak a sequence k and so do  $s_2$ 's next transitions (black) then the next transitions' leakage from  $t_1$  and  $t_2$  must coincide as well (purple). The target leakage l does not need to be equal to the source leakage k. Table 1 (left) lists compilers employing simulations with leakage transformation (no speculative semantics) that satisfy the constant-time cube diagram.

In the speculative execution setting, compilers so far try to avoid Spectre attacks by running compiler passes that insert the mitigations discussed above. These passes are among the last passes in the compiler chain in order to avoid the removal of mitigations by other passes. They aim to eliminate speculative leakage by inserting mitigations conservatively, which entails significant performance overhead. Even worse: Efforts to improve performance were flawed, again leading to insecure executables [Patrignani and Guarnieri 2021]. Passes that insert mitigations are desirable because they free the developer from having to think about speculation: Before the compiler runs the mitigation pass, the semantics can be considered speculation-free. However, recent research suggests that in order to obtain minimal performance overhead, the developer needs an interface to control inserted mitigations [Shivakumar et al. 2023]. This means a new proof method for compilation is needed that works when both source and target program operate under speculative execution semantics.

To the best of our knowledge, Patrignani and Guarnieri [2021] is the only work so far to (dis-)prove compiler correctness under speculative execution semantics. The authors target specifically compiler passes that insert mitigations and discovered the aforementioned flaws in fence insertion and speculative load hardening. Being tailored towards mitigations, they employ assumptions on the setting that do not hold in general and that we overcome in our development. We detail the differences to our work in Table 1 (right): **Property:** The first difference lies in the property ensuring side-channel security. While speculative non-interference preservation (SNiP) is the goal,

Table 1. Left: Compilers that preserve side-channel security under leakage semantics; Compcert [Leroy 2009], Jasmin [Barthe, Grégoire, Laporte, and Priya 2021]. Right: Proof methods for compilers with speculative execution semantics; Ex. Spectres [Patrignani and Guarnieri 2021]. Green parameters are more expressive.

|               | Compcert | Jasmin | Ex. Spectres    | This Paper |

|---------------|----------|--------|-----------------|------------|

| Property      | NiP      | NiP    | STsP            | SNiP       |

| Simulation    | LT-Sim   | LT-Sim | LO-Sim          | DT-Sim     |

| Speculation   | _        | _      | SW, M, TO       | US, ST     |

| Non-Det       | No       | No     | No              | Yes        |

| Spec Source   | _        | _      | PHT             | PHT        |

| Memory Safety | S        | S      | U               | S          |

| Passes        | Full     | Full   | SLH & Fence Ins | DC & RA    |

their proof method preserves speculative taint safety (STsP). Taint safety is a safety property that soundly approximates non-interference. While STsP is not an approximation of SNiP, the method is appropriate for analyzing mitigation passes. Our method is designed to prove SNiP, instead. Speculation and Non-Det: A bigger difference is the speculative execution semantics: They assume a speculation window (SW) that limits the number of steps speculatively executed after a misprediction before a rollback occurs. Speculation windows are a restriction of the speculative execution semantics. While the restriction is reasonably chosen with respect to current hardware, it presents an under-approximation of the speculative execution semantics. They further assume that the semantics always mispredicts branches (M) to maximize speculative execution. Mispredict semantics are no further restriction of the semantics, as maximizing speculative execution also maximizes the side-channel leakages produced. Together, these assumptions form a deterministic restriction of the full speculative execution semantics. The focus on compiler mitigations also led them to the assumption that the source language is speculation-free, meaning the speculative semantics are target program only (TO). In this paper, we deal with full, unbounded speculative execution semantics (US) and the induced non-determinism in both source and target semantics (ST). Memory: Our work is presented for structured memory (S) and the assumption that source programs are memory safe when executed under speculation-free semantics. Memory safety is a common assumption for compilers, as unsafe memory accesses are usually considered undefined behavior in source semantics. Our proof method also works with unstructured memory (U), but we also present a static analysis whose presentation immensely benefits from structured memory. This led us to present all of our work with structured memory as the concepts behind the proof method stay the same. Simulation: Mitigations insert speculation barriers and do not change the code otherwise. As the source program in Patrignani and Guarnieri [2021] does not speculate, the leakages of the source program will still be fully present and unchanged in the target program. Because the target program is executed with speculative execution semantics, there can, however, be additional leakages present in the target program. This leads their work to consider leave-out simulations (LO-Sim), where source leakages are equal to target leakages with additional speculative leakages. For general compiler transformations and unbounded speculation, we introduce the more general directive transforming simulations (DT-Sim). Passes: Their work targets the compiler passes that insert the software mitigations against spectre from above: Speculative load hardening and fence insertion. Our work targets two general-purpose compiler transformations: Dead code elimination (DC) and transformations from the register allocation phase (RA).

### 1.2 Contributions

In this paper, we present snippy simulations, a novel proof method for preservation of noninterference under speculative execution semantics. The main challenge to overcome with speculation is the non-determinism in directive semantics. First, the definition of simulations becomes more involved: Deterministic semantics have the advantage that simulations are always bi-simulations [Milner 1971]. A simulation for deterministic semantics synchronizes the (singular) execution of the source program and the execution of the target program. For non-deterministic semantics such as speculative execution semantics, each of the target program's executions must be synchronized with a source program's execution. Second, similar to how compilers do not preserve leakage, they also modify where the attacker can steer the computation: A sequence of directives to steer execution on the source program may be unfit to steer any execution on the target program (the compiler may change instructions and with them the available directives to steer execution also change). We address this issue by introducing the new concept of directive transformations. Directive transformations match every executable sequence of directives in the target program with a sequence of directives executable in the source program. We then embed directive transformations into a new constant-time cube for speculative execution semantics (Figure 1, right). It is our contribution to make the constant-time cube applicable for speculative semantics.

We demonstrate our proof method on two compiler transformations: Dead code elimination and register allocation. This is the first time that these compiler passes have been formally analyzed under speculative execution semantics and to our surprise, we found a serious vulnerability in the transformations performed during the register allocation phase. The register allocation phase is located in the compiler chain where a hardware-independent intermediate representation is replaced by a concrete ISA. It transforms virtual registers into hardware registers and has to spill excess registers to the stack: In Code 1, the framed instructions constitute a spill of the register bytes. The program before register allocation (without Lines 3 and 7) has no side-channel leakage of sensitive data under speculative execution semantics. The program after register allocation (with Lines 3 and 7) is vulnerable to the Spectre attack presented above. This vulnerability is not unique to a singular register allocator, but more generally stems from the spilling transformation performed in this phase. In order to fix the transformations performed, we present a novel static analysis on a product of source program (before register allocation) and target program (after register allocation) that finds problematic speculative leakages introduced by spilling transformations. We then fix the problematic transformations by inserting as few mitigations as possible. The fix is automated and applies to every existing register allocator. We then show that the fixed transformations are secure by once more applying our proof method.

In short, we address the problem of non-interference preservation for compiler passes under speculative execution semantics. We make the following contributions:

- ▶ We develop a proof method for non-interference preservation *under speculative execution semantics* based on simulation relations. Technically, we address non-determinism from speculation with *directive transformations*.

- ▶ We *demonstrate* our proof method on dead code elimination.

- ► We show that *register allocation does not preserve non-interference* under speculative execution semantics. We confirm this for all register allocators of the LLVM compiler on code from the widely used libsodium cryptographic library.

- ▶ We propose a static analysis that *finds and automatically fixes* the vulnerabilities introduced by any register allocator. We apply our proof method to show that the fixed transformation preserves speculative non-interference.

Outline. Section 2 introduces our formulation of speculative execution semantics with leakages and directives. Section 3 defines speculative non-interference preservation (SNiP). Our proof method is presented in Section 4, and we apply it in Section 5 to prove that dead code elimination preserves non-interference. We then analyze the vulnerability we found in the register allocation transformations and present our fix in Section 6. We finish with related works in Section 7 and discuss future prospects in Section 8.

# 2 Language Model

We introduce our programming language and its speculative execution semantics. A program is a mapping  $P: PC_P \to Inst$  from program counters to instructions. The initial program counter is init  $\in PC_P$ . Instructions  $i \in Inst$  are of the following form. We denote registers by  $a, b, c, d \in Reg$  and memory variables by  $\mathbf{a}, \mathbf{b} \in Var$ . The subscripts  $\mathbf{sc} \in PC_P$  are the successors of i. We may also call  $\mathbf{sc}$  a successor of  $\mathbf{pc}$  constant, if it is a successor of  $\mathbf{pc}$  pc.

```

i \in \mathit{Inst} \ ::= \ \mathsf{ret} \ | \ \mathsf{nop}_{\mathsf{ssc}} \ | \ a := b \oplus c_{\mathsf{ssc}} \ | \ a := \mathbf{a}[b]_{\mathsf{ssc}} \ | \ \mathbf{a}[b] := c_{\mathsf{ssc}} \ | \ \mathsf{br} \ b_{\mathsf{ssc}_\mathsf{t}, \mathsf{scf}} \ | \ \mathsf{sfence}_{\mathsf{ssc}} \ | \ \mathsf{s1h} \ a_{\mathsf{ssc}} \ | \ \mathsf{s1h} \ a_{\mathsf{s1h}} \ | \ \mathsf{s1h} \ a_{\mathsf{s1h}} \ | \ \mathsf{s1h} \ a_{\mathsf{s1h}} \ | \ \mathsf{s1h} \ | \ \mathsf{s1h} \ a_{\mathsf{s1h}} \ | \ \mathsf{s1h} \ |

```

The instructions are return (or exit), no-op, assignment, load, store, conditional branching, and the software mitigations for Spectre, speculation fences and speculative load hardening.

Semantics. We introduce two semantics: Speculation-free  $s \xrightarrow{\delta:\lambda} t$  (Rules 2.1) and speculative  $s \xrightarrow{\delta:\lambda} T$  (Rules 2.2). The transitions are labelled by leakage  $\lambda \in Leak$  and directives  $\delta \in Direct$ . Our leakages stem from the constant-time leakage model which leaks the addresses of memory accesses as well as branching conditions. Directives resolve non-determinism for the speculative semantics, i.e. when speculation starts and ends or where unsafe memory accesses (out-of-bounds) actually access memory. Directives are considered under the attacker's control.

A speculation-free state is a tuple  $(pc, \rho, \mu) \in State$  that tracks the program counter  $pc \in PC$ , register contents  $\rho : Reg \to Val$ , and memory  $\mu : Mem \to Val$ . The semantics is given in Rules 2.1 and is fairly standard. Memory is structured and without dynamic allocation. Each variable **a** has static size and for an offset address  $n \in Adr \subseteq Val$ , we write  $n \in |\mathbf{a}|$  to indicate that n lies within  $\mathbf{a}$ 's size. The memory is  $Mem = \{(\mathbf{a}, \mathbf{n}) \mid \mathbf{n} \in |\mathbf{a}|\}$ . Following the leakage model, loads (LOAD and LOAD-UNSAFE) and stores (STORE and STORE-UNSAFE) leak the accessed address used via LD  $\mathbf{n}$  and ST  $\mathbf{n}$ , and branching (BRANCH) leaks its condition with BR  $\mathbf{b}$ . The directives LU  $\mathbf{b}$   $\mathbf{m}$  (LOAD-UNSAFE) and SU  $\mathbf{b}$   $\mathbf{m}$  (STORE-UNSAFE) let the attacker control the address for unsafe memory accesses.

The source of speculation are  $br\ b$  instructions triggering branch-prediction (PHT). Our semantics models speculation only for misspeculated branches. The reason for this is that a correctly predicted branch will later commit and the resulting architectural state and the observable leakages will coincide with an execution that did not speculate in the first place. With no difference in correct speculation and speculation-free execution there is no need to model correctly speculated branches separately, and we will use the terms speculation and misspeculation interchangeably. Speculation thus starts with a branch misprediction, and later ends with a rollback to the state before speculation. A speculating state tracks all active mispredictions in a stack of states  $s, r, \ldots \in s$  state s. The semantics  $s \xrightarrow{\delta:\lambda} T$  is provided in Rules 2.2. With s0, we access s1 instruction s1 pc, when s2 (pc, s2, s3). The mitigation instructions sfence and s3 are speculation sensitive, as their semantics depend on whether the current state is speculating. Their semantics is according to our explanation in Section 1: A speculation fence sfence disallows speculation, so sfence only executes in states currently not speculating. SLH performs speculative load hardening s3 h s4, which wipes a register only if the state is currently speculating. The remaining instructions

<sup>&</sup>lt;sup>4</sup>This means our semantics allows for another speculation immediately after rollback. This could be avoided with an additional flag to store whether a state has already been mispredicted.

RULES 2.1: SPECULATION-FREE SEMANTICS

$$\begin{array}{c}

NOP \\

P \text{ pc} = \text{nop,}_{sc} \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \bullet} (sc, \rho, \mu)

\end{array}$$

$$\begin{array}{c}

ASGN \\

P \text{ pc} = a := b \oplus c,_{sc} \quad v = \rho b \oplus \rho c \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \bullet} (sc, \rho, \mu)

\end{array}$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad v = \rho b \oplus \rho c \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \bullet} (sc, \rho [a \mapsto v], \mu)

\end{array}$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad n = \rho b \in |a| \quad v = \mu a n \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \text{STORE}} (sc, \rho, \mu [(a, n) \mapsto v])

\end{array}$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad n = \rho b \in |a| \quad v = \mu a n \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \text{STD}} (sc, \rho [a \mapsto v], \mu)

\end{array}$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad n = \rho b \in |a| \quad v = \mu a n \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \text{STD}} (sc, \rho [a \mapsto v], \mu)

\end{array}$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad n = \rho b \in |a| \quad v = \mu a n \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \text{STD}} (sc, \rho [a \mapsto v], \mu)

\end{array}$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad n = \rho b \in |a| \quad v = \mu a n \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \text{STD}} (sc, \rho [a \mapsto v], \mu)

\end{array}$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad n = \rho b \in |a| \quad v = \mu a n \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \text{STD}} (sc, \rho [a \mapsto v], \mu)

\end{array}$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad n = \rho b \in |a| \quad v = \mu a n \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \text{STD}} (sc, \rho [a \mapsto v], \mu)

\end{array}$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad n = \rho b \in |a| \quad v = \mu a n \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \text{STD}} (sc, \rho [a \mapsto v], \mu)

\end{array}$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad n = \rho b \in |a| \quad v = \mu a n \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \text{STD}} (sc, \rho [a \mapsto v], \mu)

\end{array}$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad n = \rho b \in |a| \quad v = \mu a n \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \text{STD}} (sc, \rho [a \mapsto v], \mu)

\end{array}$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad n = \rho b \in |a| \quad v = \mu a n \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \text{STD}} (sc, \rho [a \mapsto v], \mu)$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad n = \rho b \in |a| \quad v = \mu a n \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \text{STD}} (sc, \rho [a \mapsto v], \mu)$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad n = \rho b \in |a| \quad v = \mu a n \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \text{STD}} (sc, \rho, \mu) \xrightarrow{\bullet : \text{STD}} (sc, \rho, \mu)$$

$$\begin{array}{c}

DOAD \\

P \text{ pc} = a := a [b],_{sc} \quad n = \rho b \in |a| \quad v = \mu a n \\

\hline

(pc, \rho, \mu) \xrightarrow{\bullet : \text{STD}} (sc, \rho, \mu) \xrightarrow{\bullet : \text{STD}}$$

are *speculation insensitive*. STEP executes them on the currently speculating state, i.e. the top-most state in the stack of states. The directives that determine whether a misprediction happens or not are SP and BR. SP demands misprediction performed by SPEC. A copy of the current state is pushed on top of the current state and the program counter is set to the incorrect branch. Otherwise, BRANCH executes on directive BR for a correct branching. ROLLBACK rolls back execution to before the last misprediction. It can be triggered with a RB directive in any state that is currently speculating. There is no bound on the length of a speculation.

We write  $S \xrightarrow{d:l}^* T$  for finite executions and  $S \xrightarrow{d:l} \infty$  for diverging executions. We use l and d for both finite and infinite sequences, i.e.  $l \in Leak^* \cup Leak^\infty$  and  $d \in Direct^* \cup Direct^\infty$ . We call any (init,  $\rho$ ,  $\mu$ ) initial and (pc,  $\rho$ ,  $\mu$ ) with P pc = ret final. The behavior of a program consists of the directives and events along any execution from an initial state. The speculation-free semantics is deterministic, so its behavior is a single execution; the speculative behavior is non-deterministic and its behavior forms a set of executions.

$$\mathsf{Beh}\,P\,s\ \triangleq\ \begin{cases} (d\!:\!l) & s\xrightarrow{d\!:\!l}^*t,t \text{ final} \\ (d\!:\!l) & s\xrightarrow{d\!:\!l}^*\infty \end{cases} \qquad \mathsf{SBeh}\,P\,S\ \triangleq\ \begin{cases} (d\!:\!l)\mid S\xrightarrow{d\!:\!l}^*T,T \text{ final} \rbrace \\ \cup \{(d\!:\!l)\mid S\xrightarrow{d\!:\!l}^*\infty \} \end{cases}$$

We call P safe if no memory access is unsafe, i.e. for every initial state s no directives Lu a n, su a n occur in the speculation-free behavior Beh P s. For the remaining paper we assume safe programs. Note that this does not mean that speculating memory accesses need to be safe. As seen in Code 1, Spectre Attacks utilize the fact that safe programs are not safe under speculative semantics.

Code 2 contains a simplified version of Code 1. The secret is already in a register  $\rho$  secret = v and to be stored to buf at offset b. Assume the offset is out of bounds,  $\rho b = 8 \notin |buf|$ . From a state  $s = (2, \rho, \mu)$ , where the first instruction was already executed, i.e.  $\rho = f \neq 0$ , the following transitions are available: First, a speculation is started with SPEC and s is copied with program counter set to the incorrect branch 3. Next, Store-unsafe executes on directive su stk 0,  $\mu' = \mu[(stk, 0) \mapsto v]$ . The LOAD then brings

```

a = (b < buf_size)

br (a)_{3,4}

buf[b] = secret

bytes = stk[0]

br (bytes)_{6.6}

ret

```

Code 2. Simplified Code 1

the secret to a register,  $\rho' = \rho$  [bytes  $\mapsto$  v]. Finally, Branch leaks whether the secret is 0,

```

s \xrightarrow{\text{SP:BR} f} s.(3, \rho, \mu) \xrightarrow{\text{SU} \text{ stk } 0:\text{ST } 8} s.(4, \rho, \mu') \xrightarrow{\bullet: \text{LD } 0} s.(5, \rho', \mu') \xrightarrow{\text{BR:BR} \text{ v=0}} s.(6, \rho', \mu').

```

Speculative semantics exhibit two important properties: First, due to the constant-time leakage model, speculative semantics reveal the program counter to the attacker: The program counter can be deduced from the leakage of conditionals in rules Branch and Spec. Second, directives resolve all non-determinism introduced by speculation. To express the first property, we write  $S \equiv T$  to mean that S and T are at the same program point. For speculation-free states,  $s \equiv pc$  means that s is at program counter pc,  $s = (pc, \rho, \mu)$ . Then,  $s \equiv t$  means that s and t share the program counter,  $s \equiv pc \equiv t$ . For speculating states, we write  $S \equiv T$  if each pair of configurations in their speculation stack is at the same program point. Formally,  $\varepsilon \equiv \varepsilon$ , and  $S.s \equiv T.t$  if  $S \equiv T$  and  $s \equiv t$ . The following two lemmas express the properties.

Lemma 1 (Program-Counter-Leakage). If two same-point states  $S_1 \equiv S_2$  execute with the same directives and leakages,  $S_1 \stackrel{d:l}{\longrightarrow} T_1$ ,  $S_2 \stackrel{d:l}{\longrightarrow} T_2$ , then the resulting states are also same-point,  $T_1 \equiv T_2$ .

Lemma 2 (Directive-Determinism). For all S and  $\delta$  there exist at most one T and  $\lambda$  with  $S \xrightarrow{\delta : \lambda} T$ .

*Notation.* Similar to how we access the current instruction with P s, we write f s instead of f pc when  $s = (pc, \rho, \mu)$  for any  $f : PC \to A$ . Further, we extend not only the  $\equiv$ -relation to speculating states, but any relation  $R \subseteq State \times State$  is extended to a relation on SState in the obvious way:  $\varepsilon$  R  $\varepsilon$  and S.s R T.t, if S R T and s R t.

## **Non-intereference Properties**

We define non-interference and non-interference preservation for our speculative semantics. We require the initial state's memory to be partitioned into public and sensitive data through a security level assignment sec:  $Var \rightarrow SecLvl$  to a lattice  $SecLvl = (\{L, H\}, L \leq H)$ . Sensitive data (H) is considered unknown to the attacker, and we say that initial states are indistinguishable to the attacker, (init,  $\rho$ ,  $\mu$ ) =<sub>sec</sub> (init,  $\rho$ ,  $\mu'$ ), when the memory coincides on all variables considered public. That is, for all  $\mathbf{a} \in Var$  with  $\sec \mathbf{a} = \mathsf{L}$ ,  $\mu \mathbf{a} = \mu' \mathbf{a}$ .

Our formulation of speculative non-interference (SNi, Definition 1) requires indistinguishable initial states  $s_1 = s_{\text{sec}} s_2$  to produce equal behavior. That means that for both initial states (i) the sequences of executable directives are the same, and (ii) for each sequence of executable directives, the observable leakage is the same. Let us explain the necessity for the first condition. As long as the second condition is satisfied, any two executions  $s_1 \xrightarrow{d:l} T_1$  and  $s_2 \xrightarrow{d:l} T_2$  will stay in the same program point  $T_1 \equiv T_2$  (Lemma 1) and synchronously execute the same instructions. If at  $T_1$ the set of executable directives is different to those in  $T_2$ , then the instruction has to be a memory access. All other instructions have the same set of executable directives, independent of register and memory contents. This means that one state executes an unsafe memory accesses (LOAD-UNSAFE or STORE-UNSAFE) while the other executes a safe memory accesses (LOAD or STORE). However, unsafe and safe memory accesses both leak the address used. A difference in executable directive thus amounts to different leakage.

DEFINITION 1 (SNi). A program is speculatively non-interferent,  $P \models SNi$ , if all indistinguishable initial states  $S_1 =_{sec} S_2$  have the same behavior SBeh  $P S_1 = SBeh P S_2$ .

Our goal is to prove preservation of non-interference for compiler transformations. We model compiler transformations [.] that map a source program P to the transformed target program [P]. Transformations may modify the structure of initial states from source program P to target program [P]. For example, a pass that realizes the architecture's calling convention relocates function parameters to specific registers. We require each pass to come with a relation  $\prec$  on initial states that identifies the initial states of [P] with the initial states of P. In order to define preservation of non-interference, the relation has to respect sec in the following sense:

DEFINITION 2. A relation  $\prec \subseteq SState_{[P]} \times SState_P$  respects sec if every initial  $t \in SState_{[P]}$  is mapped to an initial  $s \in SState_P$  with  $t \prec s$ , and for all pairs of initial states  $t_1 \prec s_1$  and  $t_2 \prec s_2$ :  $t_1 =_{sec} t_2$  if and only if  $s_1 =_{sec} s_2$ .

Speculative non-interference preservation for a transformation [.] asks whether for all source programs P,  $P \models SNi$  entails  $[P] \models SNi$ . However, defining preservation in this way leads to potentially surprising outcomes. Even if the source program P fails to be SNi, it can have some indistinguishable initial states which produce equal leakage. One would expect that a speculative non-interference preserving compiler transformation preserves this equal leakage to the target program [P]. But the above definition gives no such guarantee: If P fails to be SNi, there are no guarantees for [P] at all. To counteract that, our definition of speculative non-interference preservation is more precise [Patrignani and Guarnieri 2021]. It requires preservation of equal leakage for every pair of source program's and target program's initial states individually. In particular, this definition entails that if  $P \models SNi$  then also  $[P] \models SNi$ .

DEFINITION 3 (SNiP). A program translation [.] with sec-respecting mapping  $\prec$  is SNi-preserving, [.]  $\models$  SNiP, if all initial states  $t_1 =_{\text{sec}} t_2$  of [P] with initial source states  $t_1 \prec s_1$  and  $t_2 \prec s_2$  of equal behavior SBeh  $P s_1 = \text{SBeh } P s_2$  also have equal target behavior, SBeh [P]  $t_1 = \text{SBeh } [P] t_2$ .

# 4 Proving Speculative Non-interference Preservation

We present our proof method for speculative non-interference preservation. We introduce *snippy simulations* which ensure that a code transformation preserves speculative non-interference:

THEOREM 2. If for all P there is a snippy simulation  $(\prec, \lhd)$  between [P] and P, then [.]  $\models$  SNiP.

In order to reach that goal, we first define simulations that transform directives to cope with the fact that compilers do not preserve executable sequences of directives. We then introduce the constraints a snippy simulation needs to additionally satisfy and finally prove Theorem 2. This reduces proving a transformation SNiP to proving that it has a snippy simulation for each program P. In Section 5, we show how to craft a snippy simulation that is parametric in P, reducing proof effort to a once-and-for-all proof.

## 4.1 Simulation with Directive Transformation

The new feature in our work is *directive transformation*. Conceptually, a simulation between the target program [P] and the source program P shall replay any execution of [P] in P. A directive sequence d selects a single execution in [P] (Lemma 2). Our simulation wants to select a corresponding execution in P. However, the directives d may not be executable in P, or it might select an inappropriate execution. Instead, a different sequence of directives may be necessary on the source program, since transformations [.] are not designed to preserve them.

<sup>&</sup>lt;sup>5</sup>One could also have a second security assignment on the target program, but for simplicity we assume they are the same.

Code 3. Example code transformation from dead code elimination.

Example 3. We accompany our formal development with the example transformation in Code 3, where an unnecessary  $\mathbf{a} := \mathsf{buf}[\mathbf{i}]$  instruction is replaced by a nop. Consider an initial target state  $t = (\mathbf{a}, \rho, \mu)$  where  $\rho \ \mathbf{i} \notin |\mathsf{buf}|$ , and the source state  $s = (1, \rho, \mu)$ . The directives  $\mathsf{SP}.\bullet.\bullet$  are executable from t. But the same sequence cannot be executed from s: An unsafe load necessitates a directive  $\mathsf{LU}\ \mathbf{a}\ \mathsf{m}$  for any  $\mathbf{a}$  and  $\mathsf{m}$ . Thus, a transformed sequence of directives  $\mathsf{SP}.\mathsf{LU}\ \mathbf{a}\ \mathsf{m}.\bullet$  is executed.

A simulation with directive transformation (dt-sim) is a relation on states  $T \prec S$  where a target state  $T \in SState_{[P]}$  is related to a source state  $S \in SState_P$ . The directive transformation is a family of relations  $\triangleleft_{T \prec S} \subseteq Direct^* \times Direct^*$ . We characterize dt-sim in Rules 4.1. Consider any states  $T \in SState_{P}$  and  $S \in SState_{P}$  with  $T \prec S$ . To express that T is simulated by S means the following: Either both states are final (FINAL), or we have to explore all sequences of executable directives  $T \xrightarrow{d:l} V$  in [P] up to some bound (TGT). For each explored sequence of directives we apply the directive transformation  $\triangleleft_{T \triangleleft S}$ . Then, we need to replay the execution with a sequence of executable directives  $S \xrightarrow{e:k} U$  in P (SRC), so that  $V \prec U$ . Formally, we write  $\langle \prec, \triangleleft \vdash T \prec_t S : d \rangle$  to express that we are exploring executions in [P], have already seen a sequence of directives d and arrived at target state T. We can now either bound the exploration with DIRECT-TF, or continue exploration via TGT. With DIRECT-TF we look up a directive transformation for the explored d and swap to  $\langle \prec, \triangleleft \vdash V \prec_s S : e \rangle$ . This states that we are seeking to replay the explored sequence with its transformation e from S. If e is executable  $S = e^{i \cdot k}$ , U in P, COIND checks that the states reached from exploration in [P] and replay in P are again related,  $V \prec U$ . The notions of  $\lceil \prec \rceil$  and  $\lceil \prec \rceil$  make sure that both exploration in [P] and replaying in P take at least one execution step. The guarded version | requires at least one application of TGT or SRC to become the unguarded version | | Only then, DIRECT-TF and COIND become applicable. We write  $[\prec]$  for any of  $[\prec]$  or  $[\prec]$ .

DEFINITION 4 (dt-sim). A simulation with directive transformation  $(\prec, \lhd)$  consists of a relation  $\prec \subseteq SState_{[P]} \times SState_P$  and a family  $\lhd = (\lhd_{T \prec S})_{(T,S) \in \prec}$  so that for all initial  $t \in SState_{[P]}$ , there is an initial  $s \in SState_P$  with  $t \prec s$ , and for all  $T \prec S$ ,  $\langle \overrightarrow{| \prec} | \lhd_{T \prec S} \vdash T \prec_t S : \varepsilon \rangle$  can be proven in Rules 4.1.<sup>6</sup>

Example 4. Consider once again the transformation in Code 3 and the initial states t and s from Example 3. Further, let  $u=(4,\rho',\mu)$  and  $v=(d,\rho',\mu)$  with  $\rho'=\rho[a\mapsto 0]$ . We want to prove that  $t\prec s$  is justified, i.e. we need to construct  $\triangleleft_{t\prec s}$  so that  $\langle {} \checkmark, \triangleleft_{t\prec s} \vdash t \prec_t s : \epsilon \rangle$  is derivable. We drop the subscript and just write  $\triangleleft$ . Exploration via TGT yields (among others) two sequences of directives executable from t in  $[P]: sp. \bullet. \bullet$  as in Example 3 and Br. The corresponding execution takes us to  $t \xrightarrow{sp. \bullet. \bullet: BR f. \bullet. \bullet, *} t.v$  and  $t \xrightarrow{BR:BR}, v$ , respectively. After exploration with TGT, we are thus left to prove  $\langle {} \checkmark, {} \lor t.v \prec_t s : sp. \bullet. \bullet \rangle$  and  $\langle {} \checkmark, {} \lor t.v \prec_t s : sr. \bullet. \bullet \rangle$ . For the first sequence, we transform the directives as in Example 3: sp.lu sec  $0.\bullet$   $\triangleleft$  sp.  $\bullet$ . For the other case, we do not need a transformation, so Br  $\triangleleft$  Br. With direct-tr, we are left with deriving  $\langle {} \checkmark, {} \lor t.v \prec_s s : sp.lu sec 0.\bullet \rangle$  and  $\langle {} \checkmark, {} \lor t.v \prec_s s : sp.lu sec 0.\bullet \rangle$  and  $\langle {} \checkmark, {} \lor t.v \prec_s s : sp.lu sec 0.\bullet \rangle$  and  $\langle {} \checkmark, {} \lor t.v \prec_s s : sp.lu sec 0.\bullet \rangle$  and  $\langle {} \lor, {} \lor t.v \prec_s s : sp.lu sec 0.\bullet \rangle$  and  $\langle {} \lor, {} \lor,$

$<sup>^6</sup>$ Our way to define simulations is inspired by recent work to unify stuttering [Cho et al. 2023].

$$\langle T \prec_{\mathsf{t}} S \rangle \xleftarrow{d} \langle V \prec_{\mathsf{t}} S \rangle \xleftarrow{e \mathrel{\triangleleft} d} \langle V \prec_{\mathsf{s}} S \rangle \xleftarrow{e} \langle V \prec_{\mathsf{s}} U \rangle$$

to state that the proof tree contains the nodes  $\langle \begin{bmatrix} -1 \\ -1 \end{bmatrix} \triangleleft_{S \prec T} \vdash V \prec_t S : d \rangle$ ,  $\langle \begin{bmatrix} -1 \\ -1 \end{bmatrix} \triangleleft_{S \prec T} \vdash V \prec_s S : e \rangle$ , and  $\langle \begin{bmatrix} -1 \\ -1 \end{bmatrix} \triangleleft_{S \prec T} \vdash V \prec_s U : \varepsilon \rangle$  on one path. In particular, this means that  $T \xrightarrow{d:l} V$  and  $S \xrightarrow{e:k} U$  for appropriate l, k, and  $e \triangleleft_{T \prec S} d$ . We define a synchronized transition relation that executes both in a single step.

DEFINITION 5. Given a simulation ( $\prec$ ,  $\triangleleft$ ), its simulation interval transition is defined by Rule SYNC.

$$\hookrightarrow$$

$\hookrightarrow$   $\prec \times Direct^* \times Leak^* \times Direct^* \times Leak^* \times \prec$

SYNC further defines the transition relations  $\vdots_s$  and  $\vdots_t$  as the projection of simulation intervals to source and target program. Transitive closures of the transition relations are defined as usual. We say that a simulation is lock-step if simulation intervals are single step:  $\vdots_t, \vdots_s \subseteq \vdots$ .

*Example 5.* The simulation intervals resulting from Example 4 for  $t \prec s$  are:

$$(s,t) \xrightarrow{\text{SP.LU secret } 0. \bullet : \text{BR f.LD } n. \bullet \triangleleft \text{ Sp.} \bullet \bullet : \text{BR f.} \bullet \bullet} (s.u,t.v) \qquad (s,t) \xrightarrow{\text{BR : BR f.} \triangleleft \text{ BR : BR f.}} (u,v)$$

The following lemma states that our formulation of simulations is sound. That is, we find all of [P]'s behavior in the projection of the simulation interval transition relation  $\vdots$ <sub>t</sub>. This lets us perform (co-)induction on SBeh [P] S with  $\vdots$ <sub>t</sub> rather than  $\vdots$ <sub>t</sub>, which we will utilize in our proof of Theorem 2. The same is not true for the source program's behavior and  $\vdots$ <sub>s</sub>.

$$\text{Lemma 3. } \textit{If $T$ occurs in} \prec, \text{SBeh } [P] \ T = \{(d:l) \mid T \xrightarrow{d:l} {}^*_{t} X, X \textit{ final}\} \ \cup \ \{(d:l) \mid T \xrightarrow{d:l} {}^*_{t} \infty\}.$$

## 4.2 Snippy Simulations

So far, simulations are very liberal: Simulation merely require that a sequence of directives in [P] can be transformed via  $\triangleleft$  into a sequence of directives in P. The length and contained directives can change when applying  $\triangleleft$  and there are no restrictions on how the leakage changes when applying  $\triangleleft$ . In this section, we establish snippy simulations, a constant-time cube constraint [Barthe, Grégoire, and Laporte 2018] on simulations for speculative semantics that entails SNiP when satisfied.

The intuition for snippy simulations can be explained as follows. In order to prove that a transformation [.] satisfies SNiP, we are given a source program P and the target program [P], as well as four initial states: Two target initial states  $t_1 \equiv t_2$  and two simulating source states  $t_1 \prec s_1$  and  $t_2 \prec s_2$ , so that SBeh  $P s_1 = \text{SBeh } P s_2$ . The goal is to prove that the equality of behavior carries over to the target program. Given a simulation  $(\prec, \lhd)$  we so far know how to replay any sequence of directives

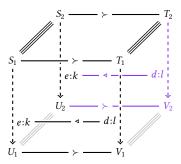

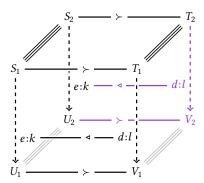

Fig. 2. Whenever the black conditions are met, a snippy simulation ≺ also explores the purple execution and simulates it by the source execution. Gray conditions follow from the semantics.

so far know how to replay any sequence of directives d from  $t_1$  transformed on  $s_1$  (Lemma 3). Consider a simulation interval  $(s_1, t_1)$   $\xrightarrow{e:k \land d:l} (U_1, V_1)$ . Due to same behavior of  $s_1$  and  $s_2$ , the source directives can also be executed from  $s_2$ ,  $s_2$   $\xrightarrow{e:k} U_2$ . Snippy simulations now state that, in such a situation, the simulation interval for  $s_2$  and  $t_2$  also contains  $(s_2, t_2)$   $\xrightarrow{e:k \land d:l} (U_2, V_2)$ . That means,  $t_2$  can also execute d and produce the same leakage. And further,  $(\prec, \lhd)$  does also explore d from  $t_2$ , not a longer or shorter sequence. Figure 2 demonstrates the constraint in the general case, where states need not be initial. The simulation interval of  $S_1$  and  $S_2$  and the ability for another source state  $S_2$  to mimic the behavior are in black. The constraint is in purple:  $(\prec, \lhd)$  has to also provide the same simulation interval for any other state  $S_2$  at the same program point as  $S_2$ . With snippy simulations defined, we conclude the section with the proof of Theorem 2.

DEFINITION 6. A snippy simulation  $(\prec, \lhd)$  is sec-respecting and satisfies the diagram in Figure 2. That is, for all  $S_1 \equiv S_2$  and  $T_1 \equiv T_2$  with  $T_1 \prec S_1$ ,  $T_2 \prec S_2$ , and  $(S_1, T_1) \xrightarrow{e:k \lhd d:l} (U_1, V_1)$ ,

$$S_2 \xrightarrow{e:k*} U_2$$

implies the existence of  $V_2$  with  $(S_2, T_2) \xrightarrow{e:k \triangleleft d:l} (U_2, V_2)$ .

PROOF OF THEOREM 2. Consider a program P and a snippy simulation  $(\prec, \lhd)$ . We need to prove the following: For all initial  $t_1 =_{\text{sec}} t_2$  with  $t_1 \prec s_1$  and  $t_2 \prec s_2$ : When SBeh [P]  $S_1 = \text{SBeh}$  [P]  $S_2$ , then also SBeh [P]  $S_1 = \text{SBeh}$  [P]  $S_2 = \text{SBeh}$  [P] [P

This is sufficient: Consider initial target states  $t_1 =_{sec} t_2$  as well as source states  $t_1 \prec s_1$  and  $t_2 \prec s_2$  with SBeh  $P s_1 = SBeh P s_2$ . Initial states are all at the same program point, so the requirements of the claim are satisfied and SBeh  $[P] t_1 \subseteq SBeh [P] t_2$  holds. By symmetry, SBeh  $[P] t_1 = SBeh [P] t_2$ .

We prove our claim coinductively on SBeh [P]  $T_1$  split into simulation intervals (Lemma 3). The case of a final  $T_1$ , i.e. SBeh [P]  $T_1 = \{(\varepsilon : \varepsilon)\}$ ,  $T_2 \equiv T_1$  is final, too, and thus  $(\varepsilon : \varepsilon) \in SBeh$  [P]  $T_2$ . In the (co-)inductive case, let  $(e.d:k.l) \in SBeh$  [P]  $T_1$  with  $T_1 \xrightarrow{e:k} V_1$  from a simulation interval  $(S_1, T_1) \xrightarrow{f:m \cdot e:k} (U_1, V_1)$ . From SBeh P  $S_1 = SBeh$  P  $S_2$  follows  $S_2 \xrightarrow{f:m \cdot *} U_2$ . Lemma 1 gives  $U_1 \equiv U_2$  and same behavior of  $S_1$  and  $S_2$  entails SBeh P  $U_1 = SBeh$  P  $U_2$ . Snippyness then yields the simulation interval  $(S_2, T_2) \xrightarrow{f:m \cdot e:k} (U_2, V_2)$ , i.e.  $T_2 \xrightarrow{e:k \cdot *} V_2$ . Lemma 1 gives  $V_1 \equiv V_2$ . We can now apply (co-)induction hypothesis for SBeh [P]  $V_1 \subseteq SBeh$  [P]  $V_2$ , which implies  $(e.d:k.l) \in SBeh$  [P]  $V_2$ . Together with  $T_2 \xrightarrow{e:k \cdot *} V_2$ , we arrive at  $(e.d:k.l) \in SBeh$  [P]  $T_2$ .

## 5 Case Study: Dead Code Elimination

In this section, we prove that dead code elimination [.]<sup>dc</sup> satisfies SNiP as a demonstration of the proof method and a warm-up for the next section, where we tackle register allocation transformations. We first give a short rundown on the transformation of [.]<sup>dc</sup> before crafting a snippy simulation that is parametric in the source program P. Dead code elimination is responsible for removing instructions from P whose computed values are not utilized anywhere. It is the result of a data flow analysis that finds removable instructions. Typically, the analysis follows constant propagation in order to identify as many aliasing memory accesses as possible. To support that, we assume that load and store instructions  $a := \mathbf{a}[n]$  and  $\mathbf{a}[n] := c$  can hold a constant address  $n \in Adr$  instead of a register, where we require  $n \in |\mathbf{a}|$ . For the remaining section, fix an arbitrary program P with entry point init.

Flow analysis. The static analysis for dead code elimination is a Liveness analysis. Since we will later define our own flow analysis when fixing the weaknesses in register allocation, we recall flow analysis in a more general setting. A flow analysis searches for a fixed-point solution to a system of flow inequalities in order to obtain approximate knowledge about all executions of a program. Formally, a forward/backward flow analysis finds a solution  $\mathcal X$  to the inequalities (fwd)/(bwd), where pc and sc range over program counters so that pc is a predecessor to sc.

$$\begin{array}{ll} \mathcal{X}\,\mathrm{sc} \geq F_{\mathrm{pc}}\left(\mathcal{X}\,\mathrm{pc}\right) & \mathcal{X}\,\mathrm{pc} \geq F_{\mathrm{sc}}\left(\mathcal{X}\,\mathrm{sc}\right) \\ \mathcal{X}\,\mathrm{init} \geq \mathcal{X}_{0} & \mathcal{Y}\,\mathrm{pc} \geq \mathcal{X}_{0} & \mathit{P}\,\mathrm{pc} = \mathsf{ret} \end{array} \tag{bwd}$$

Flow values stem from a semi-lattice  $(L, \leq)$  and a solution  $X: PC \to L$  finds a flow value for each program point. In case of a forward analysis, X pc denotes the flow value at pc before the execution of P pc. For a backward analysis X pc denotes the flow value at pc after the execution of P pc. The flow value  $X_0$  is the initial flow value of entry / exit points of the program. The functions  $F_{pc}: L \to L$  are monotonic and constitute the *transfer* of the flow values along instructions.

A flow analysis can have *additional constraints*. Additional constraints are of shape X pc  $\leq l$ . They additionally require flow values of certain program counters pc not to exceed a bound  $l \in L$ . If the least solution to the flow analysis does not satisfy the additional constraints, no solution does.

Dead Code Elimination. Liveness analysis is a backward flow analysis. The flow values are the sets of registers and memory locations that are live at any given program point in that their current value could be used later. The flow lattice is  $L = \mathcal{P}(Reg \cup Mem)$ , and the initial flow value at any exit point is  $X_0 = Reg \cup Mem$ , but can be different dependent on calling conventions. The transfer functions are folklore, so we instead formulate the guarantee that comes with a solution. Note that the guarantee holds for speculative semantics, too, because the analysis is branch-independent.

PROPOSITION 6. Whenever  $s \xrightarrow{d:l}^* U.u$  in P, if Pu uses a register b, then  $b \in F_u(Xu)$ , and if Pu loads a memory location a with offset n, then  $(a, n) \in F_u(Xu)$ .

The transformation [.] dc uses a Liveness analysis solution X of the backward flow inequalities (bwd) to remove unnecessary instructions. A function  $dc: L \to Inst \to Inst$  inspects the flow value at a given program point and removes an instruction if it writes a register or memory location that is not live. The transformation of P is then defined per program point with  $[P]^{dc}$  pc = dc (X pc) (P pc).

not live. The transformation of

$$P$$

is then defined per program point with  $[P]^{ac}$  pc  $= dc (X \text{ pc}) (P \text{ pc})$

$$dc \ l \ (a \coloneqq b \oplus c_{>sc}) = \begin{cases} \mathsf{nop}_{>sc} & a \notin l \\ a \coloneqq b \oplus c_{>sc} & a \in l \end{cases}$$

$$dc \ l \ (a \coloneqq \mathbf{a}[x]_{>sc}) = \begin{cases} \mathsf{nop}_{>sc} & a \notin l \\ a \coloneqq \mathbf{a}[x]_{>sc} & a \in l \end{cases}$$

$$dc \ l \ (a \coloneqq \mathbf{a}[x] \coloneqq c_{>sc}) = \begin{cases} \mathsf{nop}_{>sc} & x = \mathsf{n}, (\mathbf{a}, \mathsf{n}) \notin l \\ \mathbf{a}[x] \coloneqq c_{>sc} & \text{otherwise} \end{cases}$$

$$dc \ l \ i = i \quad \text{for other } i$$

$$(\mathrm{pc},\rho,\mu) \prec (\mathrm{pc},\rho',\mu') \qquad \iff \qquad \begin{aligned} \forall a \in F_{\mathrm{pc}}\left(X\,\mathrm{pc}\right).\,\rho\,\,a = \rho'\,\,a \\ \land \quad \forall (\mathbf{a},\mathsf{n}) \in F_{\mathrm{pc}}\left(X\,\mathrm{pc}\right).\,\mu\,\,\mathbf{a}\,\,\mathsf{n} = \mu'\,\,\mathbf{a}\,\,\mathsf{n} \end{aligned}$$

In order to define the directive transformation  $\triangleleft_{t \prec s}$ , we need to think about the shape of simulation intervals. Because  $[.]^{dc}$  leaves the control flow fully intact, we can choose to create a lockstep simulation. With that, we can choose  $\triangleleft_{t \prec s}$  to be the identity relation on *Direct* and add transformations where  $[.]^{dc}$  replaced an instruction with nop. Let i = Ps and  $i' = [P]^{dc}t$ . We set:

For speculating states, we simply lift  $\prec$  by setting  $T.t \prec S.s$  if  $T \prec S$  and  $t \prec s$  (and  $\varepsilon \prec \varepsilon$  for the base case). For the directive transformation, we delegate to the executing states  $\triangleleft_{T.t \prec S.s} = \triangleleft_{t \prec s}$ .

THEOREM 7.  $(\prec, \lhd)$  is a snippy lockstep simulation.

PROOF. We need to prove that  $(\prec, \lhd)$  (i) is a simulation (Definition 4), (ii) is snippy (Definition 6), and (iii) respects sec (Definition 2). The first part (i) is considerably easier than in the general case, because the simulation is lockstep, i.e. both P and  $[P]^{dc}$  only perform a single step before finding new states in  $\prec$ . Consider  $T_1.t_1 \prec S_1.s_1$ ,  $T_2.t_2 \prec S_2.s_2$ ,  $T_1.t_1 \equiv T_2.t_2$   $S_1.s_1 \equiv S_2.s_2$  and  $T_1.t_1 \xrightarrow{\delta:\lambda} V_1$ , where  $t_1 \equiv t_2 \equiv s_1 \equiv s_2 \equiv \text{pc}$ . We need to show that there is  $\gamma \triangleleft_{t_1 \prec s_1} \delta$  so that  $S_1.s_1 \xrightarrow{f:\lambda} U_1$  and  $V_1 \prec U_1$ . Second we prove snippyness (ii): We additionally consider the existence of  $S_2.s_2 \xrightarrow{f:\lambda} V_2$ . We then need to show that  $T_2.t_2 \xrightarrow{\delta:\lambda} V_2$  and  $\gamma \triangleleft_{t_2 \prec s_2} \delta$  (which implies  $(s_2, t_2) \xrightarrow{\delta:\lambda \dashv \gamma:\kappa} (u_2, v_2)$ ).

We first split off the case  $\delta = \gamma = \text{RB}$ , where  $|T_1| > 0$ . For (i), we need to prove  $S_1.s_1 \xrightarrow{\text{RB}:\text{RB}} S_1$  because  $\text{RB} \triangleleft_{t_1 \triangleleft s_1}$  RB. But  $T_1 \triangleleft S_1$  implies  $|T_1| = |S_1| > 0$  which meets the premise for the transition. For (ii), additionally consider  $S_2.s_2 \xrightarrow{\text{RB}:\text{RB}} S_2$ . We need to show  $T_2.t_2 \xrightarrow{\text{RB}:\text{RB}} T_2$ . With the same argument as before,  $|T_1| = |S_1| = |S_2| = |T_2| > 0$  satisfies the premise for the transition. Proving (i) and (ii) in the case of  $\delta \neq \text{RB} \neq \gamma$  is a large case distinction on  $\langle P \text{ pc}, [P]^{\text{dc}} \text{ pc} \rangle$ .

▶  $\langle a := \mathbf{a}[b]_{ssc}, \mathsf{nop}_{ssc} \rangle$  There are two subcases:  $\rho_{s_1} b = \mathsf{n}$  is within  $|\mathbf{a}|$  or not. We present the subcase  $\mathsf{n} \notin |\mathbf{a}|$ . For (i), consider  $t_1 \xrightarrow{\bullet : \bullet} v_1$ . We need to show that  $\mathsf{LU} \, \mathbf{b} \, \mathsf{m}$  is executable in  $s_1$ , because  $\mathsf{LU} \, \mathbf{b} \, \mathsf{m} \, \triangleleft_{t_1 \prec s_1} \bullet$ . Indeed, we have  $s_1 \xrightarrow{\mathsf{LU} \, \mathsf{b} \, \mathsf{m} : \mathsf{LD} \, \mathsf{n}} u_1$  because  $\rho_{s_1} b = \mathsf{n} \notin |\mathbf{a}|$ . We also need to show that  $v_1 \prec u_1$ . From the definition of dc, we know  $a \notin X$  pc because the instruction was replaced by nop. The transfer  $F_{\mathsf{pc}} (X \, \mathsf{pc})$  is again  $X \, \mathsf{pc}$  because a load to a dead register makes no registers or memory locations live. Together with (bwd), we get  $F_{\mathsf{pc}} (X \, \mathsf{pc}) = X \, \mathsf{pc} \supseteq F_{\mathsf{sc}} (X \, \mathsf{sc})$ . Registers and memory of  $t_1$  and  $t_1$  are equal (nop) and  $t_1$  and  $t_2$  and  $t_3$  implies  $t_1 \prec t_2$  because  $t_1 \prec t_3$  implies  $t_2 \prec t_3$  because  $t_3 \not \in X \, \mathsf{pc}$  because  $t_3 \not \in X \, \mathsf{pc}$  because  $t_4 \not \in X \, \mathsf{pc}$  because  $t_5 \not \in X \, \mathsf{pc}$  because  $t_7 \not$

For (iii), we need to restrict our attention to Liveness analysis where all registers and memory locations are initially live. Every solution  $\mathcal{X}$  is easily modified to satisfy this restriction. The proof that  $\prec$  respects sec is then straightforward: For initial states t and s,  $t \prec s$  if and only if t = s.  $\Box$

$<sup>^7\</sup>mathrm{A}$  weaker formalization of sec-respecting relations would lift this restriction, but incur more presentational overhead.

## 6 Fixing Weaknesses in Register Allocation

Register allocation happens in the compilation phase that moves from an IR to the hardware instructions of the target architecture. It moves from the unbounded number of virtual registers occurring in the IR version of the program to the finite set of hardware registers. In order to do so, register allocation performs a relocation of register contents. For each program point, a subset of the virtual registers is selected to be kept as hardware registers and the remaining virtual registers are spilled to the stack. The literature describes various approaches towards selecting the set of registers to be spilled [Chaitin et al. 1981; Traub et al. 1998; Poletto and Sarkar 1999; Tichadou and Rastello 2022], leading to different transformations depending on the chosen algorithm. In this paper, we express the transformations from register allocation more generally as a set of constraints. A transformation constitutes a viable register allocation if it satisfies the constraints. Practical allocation algorithms produce viable allocations making our results apply to all of them.

We first present the constraints a register allocation transformation needs to satisfy. We then demonstrate how the transformation violates speculative non-interference preservation. We continue to develop a static analysis that finds potential violations. Finally, we fix the violations and craft a snippy simulation for the fixed transformation and prove that it satisfies SNiP.

## 6.1 Register Allocation

Register allocation transforms a source program *P* by inserting *shuffle instructions*.

$$si \in Shuffle\ Inst ::= a := b_{>sc} \mid a := stk[I]_{>sc} \mid stk[I] := b_{>sc} \mid slh\ a_{>sc} \mid sfence_{>sc}$$

The instructions extend Inst and are inserted in between the existing instructions in order to maintain the register relocation with the instructions move a := b, fill a := stk[I], and spill stk[I] := b. We also include slh a and sfence because we need them later to fix the transformation. The semantics are as expected: A move a := b relocates contents from b to a, a := stk[I] reloads a spilled register from a constant address  $l \in Adr$  in the stack, and stk[I] := b spills a register to the stack. We model the stack frame's section used for spilled registers with a fresh memory variable stk not occurring in p. We assume that stk has appropriate size to fit all spilled registers and is typed scc stk = L. Shuffle code is always straight line, so for a shuffle sequence  $sh \in Shuffle Inst^*$  we introduce the notion p pc  $sh_{ssc}$  to express that p executes sh and then ends in sc.

Constraints for a valid transformation. Register allocation inserts shuffle code between existing instructions to realize the register relocation. Formally, a target program  $[P]^{\mathrm{ra}}: PC_{[P]^{\mathrm{ra}}} \to Inst$  is a register allocation if there exist functions  $\Phi$  and  $\Psi$ . The first is an injection  $\Phi: PC_P \to PC_{[P]^{\mathrm{ra}}}$  of the original instructions of P to their counterparts in  $[P]^{\mathrm{ra}}$ . The second function is a relocation mapping  $\Psi: PC_{[P]^{\mathrm{ra}}} \to Reg \to (Reg \cup Stk)$ , where  $Stk = \{(\mathbf{stk}, \mathsf{I}) \mid \mathsf{I} \in |\mathbf{stk}|\} \subseteq Mem$  is the stack frame for spilled variables. At each program counter  $\mathsf{pc}' \in PC_{[P]^{\mathrm{ra}}}$ ,  $\Psi$   $\mathsf{pc}'$  a is the relocation of the virtual register a from P to the hardware register or stack location in  $[P]^{\mathrm{ra}}$ . The functions are subject to the following conditions. Instruction matching: The  $\Phi$ -injected instructions must operate on the same registers up to relocation by  $\Psi$ . Shuffle conformity: The relocation  $\Psi$  must conform to the (shuffle) instructions in  $[P]^{\mathrm{ra}}$ . Obeying Liveness: Every live register in P is mapped under  $\Psi$  and no location is doubly allocated. To state the conditions formally, we introduce notation for the defined and used registers of an instruction. A register b is used by b if it is written in that rule. For example,  $a := \mathbf{a}[b]$  uses  $\{b\}$  and defines  $\{a\}$ .

$$uses_i = \{b \mid b \in Reg \text{ is used by } i\}$$

$def_i = \{a \mid b \in Reg \text{ is defined by } i\}$

<sup>&</sup>lt;sup>8</sup>In general, the content of a register *a* could be relocated to multiple locations. For simplicity of presentation, we forbid that.

Code 4. An Example register allocation. Lines b and e are the inserted shuffle code.

Instruction Matching requires that source instructions from P reappear in  $[P]^{ra}$ : For every  $pc \in PC_P$  and  $pc' = \Phi$  pc, i = P pc has to match with  $i' = [P]^{ra}$  pc'. To match, the instruction i' must be the same, but registers  $b \in uses_i$  are replaced with  $\Psi$  pc'  $b \in Reg$ . Similarly, registers  $a \in def_i$  are replaced with  $\Psi$  sc'  $a \in Reg$ , where sc' is the successor of pc'. Defined registers are found in the successor's relocation, because they are live only after executing i'. All other instructions at program points  $pc' \notin img(\Phi)$  must be shuffle instructions. Given  $s \in State_P$  and  $t \in State_{[P]^{ra}}$ , we write  $s \Phi t$  when  $s \equiv pc$  and  $\Phi pc \equiv t$ . We extend the notation to  $s \Phi T$  in the expected way.

Shuffle Conformity requires that the relocation  $\Psi$  is upheld by the instructions in  $[P]^{\text{ra}}$ . Consider an instruction  $i' = [P]^{\text{ra}}$  pc' at pc'  $\in PC_{[P]^{\text{ra}}}$  and let sc' be a successor. First, registers and stack locations untouched by i' must stay at the same location in  $\Psi$ : For any register d with  $\Psi$  pc'  $d \notin \text{uses}_{i'}$  and  $\Psi$  sc'  $d \notin \text{def}_{i'}$ ,  $\Psi$  pc'  $d = \Psi$  sc' d. Second, if i' is a shuffle instruction there are additional requirements: Shuffle instructions move one source register's content from one location in  $[P]^{\text{ra}}$  to another. As a consequence, if i' is a shuffle instruction, there must be a source register a being moved and the location moved to must be free. We write free $_{r'}$  d' and free $_{r'}$  (stk, l) for d', (stk, l)  $\notin$  img( $\Psi$  r'). Dependent on i', we add the following constraints, (a is the source register):

Obeying Liveness means that all live variables in P must be allocated. There must be a Liveness solution  $\mathcal X$  (Proposition 6) for P so that for all locations  $\operatorname{pc} \in PC_P$ , all registers  $a \in \mathcal X$   $\operatorname{pc}$  live at  $\operatorname{pc}$  are allocated, i.e.  $\Psi$  ( $\Phi$   $\operatorname{pc}$ )  $a \neq \bot$ . Further, a location cannot be allocated twice, i.e. for all  $\operatorname{pc} \in PC_{[P]^{\operatorname{ra}}}$ ,  $\Psi$   $\operatorname{pc}$  forms an injection on the live registers at  $\operatorname{pc}$ .

Definition 7. A transformation from P to  $[P]^{ra}$  is a register allocation if there are instruction matching, shuffle conform, and Liveness obeying  $(\Phi, \Psi)$ .

Example 8. Code 4 contains an example register allocation. It is a simplified version of Code 1, which still exhibits the weakness of register allocation. The left program starts with a secret value in register secret and public values in b and bytes. It stores the secret into buf when the address b is in bounds of |buf|. Then, it leaks bytes at 4. The right program is after register allocation. Register allocation has inserted the spill and fill instructions b and e. The instruction injection  $\Phi$  can be seen from side by side alignment. It is the mapping  $\{1 \mapsto b, 2 \mapsto c, 3 \mapsto d, 4 \mapsto f, 5 \mapsto g\}$ . The register mapping  $\Psi$  at a and b makes no relocations:  $\Psi$  a =  $\Psi$  b =  $id_{Reg}$ . The spill instruction at b relocates bytes to the stack. It remains spilled from c to e:  $\Psi$  c bytes = ... =  $\Psi$  e bytes = (stk, 0). Further, because a is not live after 2 it is not allocated from c to g:  $\Psi$  c a = ... =  $\Psi$  g a =  $\bot$ . Instead, the register allocation reuses a in f: The fill instruction at e relocates bytes to a:  $\Psi$  f bytes = a.

## 6.2 Register Allocation is not SNiP